- 您现在的位置:买卖IC网 > Sheet目录470 > MAX11008EVC16 (Maxim Integrated)EVAL KIT MAX11008

Dual RF LDMOS Bias Controller with

Nonvolatile Memory

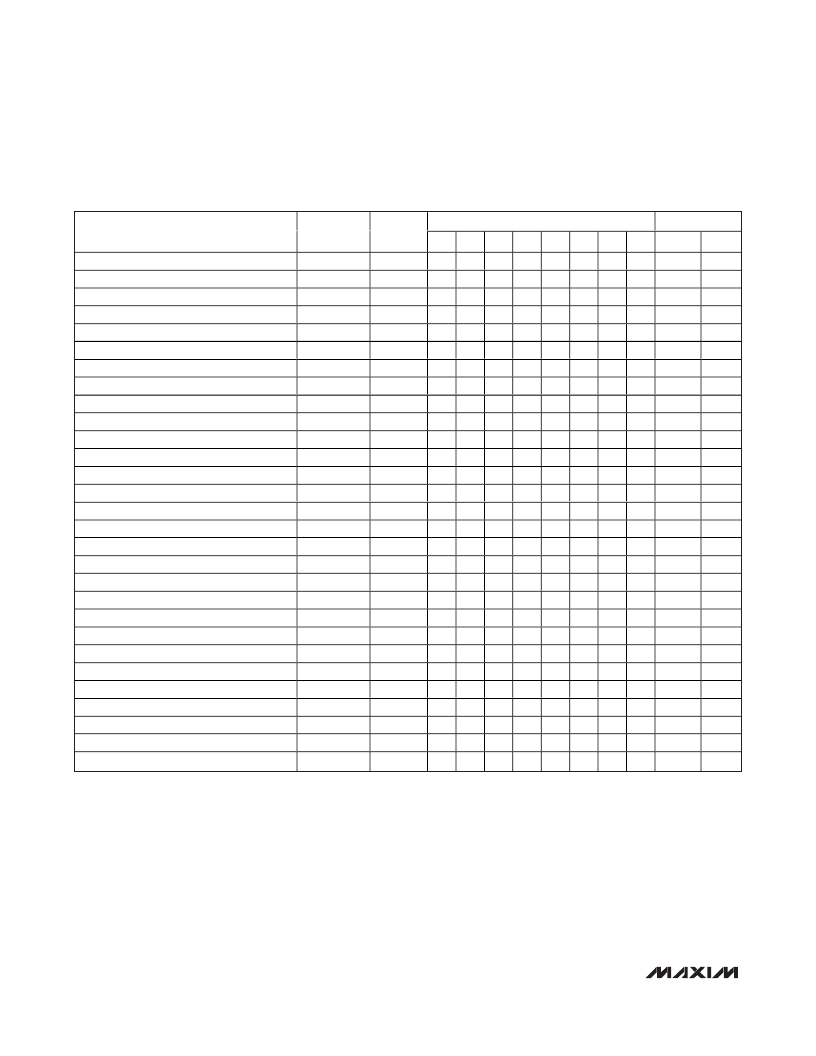

Table 6. Register Address Map

REGISTER

MNEMONIC

SEE

TABLE

C7

C6

COMMAND BITS

C5 C4 C3 C2

C1

C0

HEX CODE

WRITE READ

Channel 1 High Temperature Threshold

Channel 2 High Temperature Threshold

Channel 1 Low Temperature Threshold

Channel 2 Low Temperature Threshold

Channel 1 High Current Threshold

Channel 1 Low Current Threshold

Channel 2 High Temperature Threshold

Channel 2 Low Temperature Threshold

Hardware Configuration

Alarm Software Configuration

Software Configuration

Alarm Hardware Configuration

VSET1

VSET2

APC1 Parameter

APC2 Parameter

DAC1 Input (Write Only)

DAC2 Input (Write Only)

DAC1 Input and Output (Write Only)

DAC2 Input and Output (Write Only)

PGA Calibration Control ( Write Only)

ADC Conversion (Write Only)

Software Shutdown (Write Only)

Load DAC (Write Only)

Message (Write Only)

FIFO

Software Clear (Write Only)

LUT Streaming (Write Only)

Flag (Read Only)

TH1

TH2

TL1

TL2

IH1

IL1

IH2

IL2

HCFIG

ALMSCFIG

SCFIG

ALMHCFIG

VSET1

VSET2

HIST_APC1

HIST_APC2

IDAC1

IDAC2

IODAC1

IODAC2

PGACAL

ADCCON

SSHUT

LDAC

—

—

SCLR

—

—

7

7

8

8

9

9

10

10

11

12

13

14

15

15

16

16

17

17

18

18

19

20

21

22

23

24

25

27

26

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

R W

0

0

0

0

0

0

0

0

0

R W

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

1

1

1

1

0

1

0

1

0

0

1

1

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

0

0

1

0

0

0

0

0

1

1

1

1

0

0

1

1

0

1

0

0

0

1

0

1

0

0

1

1

1

0

1

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

1

1

0

0

1

1

0

1

0

1

1

1

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

20

28

22

2A

24

26

2C

2E

30

32

34

36

38

3C

3A

3E

58

5C

5A

5E

60

62

64

66

6E

72

74

7E

—

A0

A8

A2

AA

A4

A6

AC

AE

B0

B2

B4

B6

B8

BC

BA

BE

—

—

—

—

—

—

—

—

—

80

—

—

F6

The following properties of the register address map should be noted:

? All register data is volatile.

? Data stored in locations TH1, TH2, TL1, TL2, IH1, IH2, IL1, IL2, HCFIG, ALMSCFIG, SCFIG, ALMHCFIG, VSET1,

VSET2, IDAC1, IDAC2, IODAC1, IODAC2, PGACAL, ADCCON, SSHUT, and LDAC can be loaded from EEPROM

at power-up or after a full reset.

? Write to the FIFO register only in LUT streaming mode (see the LUT Streaming Mode section).

46

______________________________________________________________________________________

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX11014BGTM+T

IC RF MESFET AMP 48-TQFN-EP

MAX12000ETB+T

IC AMP GPS FRONT 1575MHZ 10TDFN

MAX12005ETM+T

IC SATELLITE IF SWITCH 48-TQFN

MAX1385BUTM+

IC RF LDMOS BIAS CNTRLR 48-TQFN

MAX1470EUI+T

IC RECEIVER 315MHZ 28-TSSOP

MAX1470EVKIT-315

EVAL KIT FOR MAX1470 315MHZ

MAX1471EVKIT-315

EVAL KIT FOR MAX1471 315MHZ

MAX1472EVKIT-433#

EVAL KIT MAX1472

相关代理商/技术参数

MAX11008EVKIT+

功能描述:放大器 IC 开发工具 MAX11008 Eval Kit RoHS:否 制造商:International Rectifier 产品:Demonstration Boards 类型:Power Amplifiers 工具用于评估:IR4302 工作电源电压:13 V to 23 V

MAX1100CWG

制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述:

MAX1101

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Single-Chip, 8-Bit CCD Digitizer with Clamp and 6-Bit PGA

MAX11014

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Automatic RF MESFET Amplifier Drain-Current Controllers

MAX11014_08

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Automatic RF MESFET Amplifier Drain-Current Controllers

MAX11014BGTM

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Automatic RF MESFET Amplifier Drain-Current Controllers

MAX11014BGTM+

功能描述:特殊用途放大器 Auto RF MESFET Amp Drain-Current Cntrlr RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel

MAX11014BGTM+T

功能描述:射频放大器 Auto RF MESFET Amp Drain-Current Cntrlr RoHS:否 制造商:Skyworks Solutions, Inc. 类型:Low Noise Amplifier 工作频率:2.3 GHz to 2.8 GHz P1dB:18.5 dBm 输出截获点:37.5 dBm 功率增益类型:32 dB 噪声系数:0.85 dB 工作电源电压:5 V 电源电流:125 mA 测试频率:2.6 GHz 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-16 封装:Reel